# OPERATORS MANUAL Model 2108

VXI Serial Data System Digital Resource Module

Manual Revision: 06/22/06 Manual Part Number: 2108RM003 Instrument Part Number: 30080/30150/30250

### CERTIFICATION

Talon Instruments certifies that this product met its published specifications at the time of shipment from the factory.

### WARRANTY

Talon Instruments products are warranted against defects in materials and workmanship as follows:

- (a) One year for the 2108 motherboard and all modules.

- (b) Ninety days for cables and adapters.

During the warranty period, Talon Instruments will, at its option, either repair or replace products which prove to be defective.

For warranty service or repair, this product must be returned to the Talon Instruments factory. Buyer shall prepay shipping charges to the factory and Talon Instruments shall pay shipping charges to return the product to the Buyer. However, Buyer shall pay all shipping charges, duties, and taxes for products returned to Talon Instruments from another country.

Talon Instruments warrants that its software and firmware designated by Talon for use with its instruments will execute its programming instructions when properly installed on the instrument. Talon Instruments does not warrant that the operation of the instrument, or software, or firmware will be uninterrupted or error free.

# LIMITATION OF WARRANTY

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by the Buyer, Buyer-supplied software or interfacing, unauthorized modification or misuse, operation outside of environmental specifications for the product, or improper site preparation or maintenance.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED. TALON INSTRUMENTS SPE-CIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

### **EXCLUSIVE REMEDIES**

THE REMEDIES PROVIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES. TALON INSTRUMENTS SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, IN-CIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

# **SAFETY FIRST** PROTECT YOURSELF AND THE EQUIPMENT. Follow these precautions: · Don't bypass the chassis' power cord's ground lead with two-wire extension cords or plug adapters. · Don't disconnect the green and yellow safety-earth-ground wire that connects the ground lug of the chassis power receptacle to the chassis ground terminal. • Don't energize the chassis until directed to by the installation instructions. • Don't repair the instrument unless you are a qualified electronics technician and have instructions from Talon Instruments. Pay attention to the WARNING statements. They point out situations that can cause injury or death. Pay attention to the CAUTION statements. They point out situations that can cause equipment damage. • Use ESD static control procedures when handling the 2108 or any of its modules.

# **Table of Contents**

| 1                                | Introduction                                                                               |

|----------------------------------|--------------------------------------------------------------------------------------------|

| 1.1                              | Basic Elements of Serial Interfaces 1-1                                                    |

| 1.1.1<br>1.1.2<br>1.1.3<br>1.1.4 | Serial Bus Electrical Characteristics1-1Data Clocking1-1Waveform Data1-1Control Signals1-2 |

| 2                                | Installation                                                                               |

| 2.1                              | Hardware Installation                                                                      |

| 2.1.1                            | Receiving Inspection                                                                       |

| 2.1.2                            | Returning Equipment                                                                        |

| 2.1.3                            | Preparation for Storage                                                                    |

| 2.1.4                            | Preparation for Use                                                                        |

| 2.1.4.1                          | Logical Address Selection                                                                  |

| 2.1.4.2                          | VXI Interrupt Selection                                                                    |

| 2.1.4.3                          | A24/A32 Map Selection                                                                      |

| 2.1.5                            | Installation                                                                               |

| 2.1.5.1                          | Initial Power-On                                                                           |

| 2.2                              | Software Installation                                                                      |

| 2.2.1                            | VXI Plug&Play Instrument Driver                                                            |

| 2.2.2                            | 2108 Project Development System (PDS)                                                      |

| 2.2.2.1                          | Execution Manager (EM)                                                                     |

| 2.2.2.3                          | Serial Logic Analyzer (SLA)                                                                |

| 3                                | 2108 Front Panel                                                                           |

| 3.1                              | LED Indicators                                                                             |

| 3.1.1                            | Transmitter Interconnect LED Indicator                                                     |

| 3.1.2                            | Receiver Interconnect LED Indicator                                                        |

| 3.2                              | SMA Connector                                                                              |

| 3.3                              | Power Connector                                                                            |

| 3.4                              | J1-J4 I/O Connector                                                                        |

| 3.5                              | 2108 Front Panel Mating Connectors                                                         |

| 4                                | Operation                                                                                  |

| 4.1                              | Initializing the VXI Session                                                               |

| 4.2                              | Configure the 2108 Settings and Structures 4-1                                             |

| 4.2.1                            | Defining the 2108 PDE Configuration                                                        |

| 4.2.2                            | Configure the 2108 Transmitter                                                             |

| 4.2.2.1                          | Logical Bit Settings                                                                       |

| 4.2.2.2                          | Electrical Characteristics                                                                 |

| 4.2.2.3                          | Signal Routing                                                                             |

| 4.2.2.4                          | Waveform Definition                                                                        |

| 4.2.2.5                          | Define the Bit Sequence(s)                                                                 |

| 4.2.2.5.                         | ,                                                                                          |

| 4.2.2.5.                         | 2 Programming Control Memory Tables                                                        |

| 4.4.2                   | Soft Front Panel Execution Manager 4-                                                       | -35    |

|-------------------------|---------------------------------------------------------------------------------------------|--------|

| 4.5                     | Evaluate and Analyze Results 4-                                                             | -37    |

| 4.5.1<br>4.5.2<br>4.5.3 | Transmitter Status       4-         Receiver Status       4-         Receiver Data       4- | -38    |

| 4.5.3.1                 | Receiver Data Format                                                                        | -38    |

| 4.5.3.1.1               | Record Data Format Example 4-                                                               | -39    |

| 4.6                     | Close the VXI session                                                                       | -41    |

| Appendix sary           | άΑΘ                                                                                         | 3los-  |

|                         | B                                                                                           | Serial |

# List of Figures

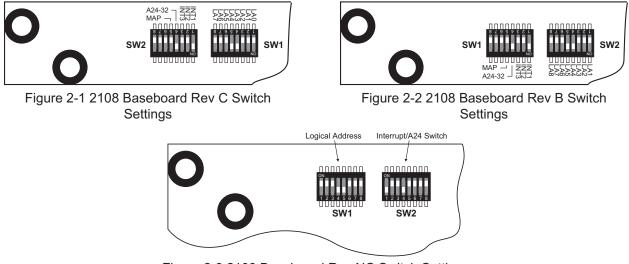

| Figure 2-1 2108 Baseboard Rev C Switch Settings  | 2-2 |

|--------------------------------------------------|-----|

| Figure 2-2 2108 Baseboard Rev B Switch Settings  | 2-2 |

| Figure 2-3 2108 Baseboard Rev NC Switch Settings | 2-2 |

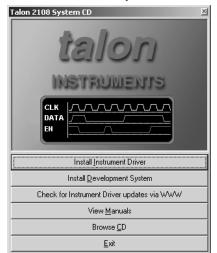

| Figure 2-4 2108 System CD Installation Menu      | 2-4 |

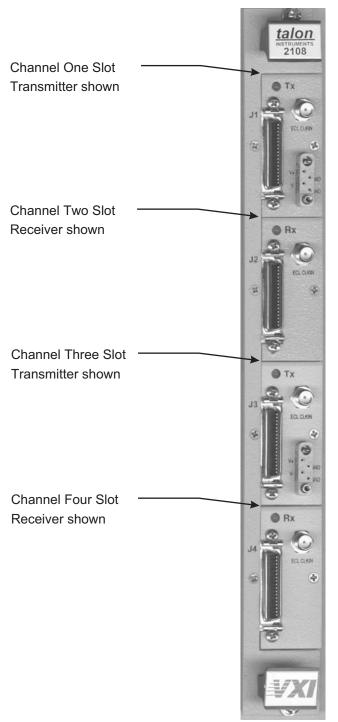

| Figure 3-1 2108 Front Panel                      | 3-1 |

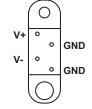

| Figure 3-2 Power Connector                       | 3-2 |

| Figure 3-3 J1-J4 Connector                       | 3-2 |

# List of Tables

| Table 3-1 Power Connector Pinouts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-2  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Table 3-2 Mating Connector Part Numbers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-3  |

| Table 3-3 J1-J4 I/O Connector Assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-3  |

| Table 4-1 Transmitter Status Bits    Image: Comparison of the status of the stat | 4-37 |

| Table 4-2 Record Data Format Bit Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-38 |

| Table 4-3 Receiver Status Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-38 |

# **1** Introduction

The Model 2108 is a flexible and capable serial bus emulator module that can be programmed to emulate a vast variety of serial bus protocols at speeds from 2Kbps to 200Mbps data rate. The flexibility of the 2108 module allows the user to fine-tune virtually all aspects of a serial bus interface, both at the electrical and logical levels.

The Model 2108 is comprised of a "C" size VXI motherboard which houses four instrument modules and four front-end signal conditioning modules. For serial emulation the instrument modules are the transmitter, 2108TX and the receiver, 2108RX. A number of interconnect modules for the 2108TX and 2108RX are available to provide signal conditioning for the various requirements imposed by different interfaces.

The Model 2108 may be configured with 1 to 4, 2108TX's, 1 to 4, 2108RX's or a combination of the two. If a 2108TX and 2108RX are installed in channel slots 1&2 or 3&4, they may be operated in a bi-directional mode.

# **1.1 Basic Elements of Serial Interfaces**

There are a variety of serial interfaces being used today in the consumer, industrial and military sectors. Although a significant percentage of these interfaces are comprised of a number of standardized serial protocols, such as USB, IEEE 1394 and MIL-STD-1553, there is still an equally large percentage composed of custom serial interfaces. This group includes not only purpose-built interfaces but also variants of the standardized protocols.

In all instances, these standard and custom serial interfaces share some very basic elements. These elements include a set of electrical characteristics, a logical protocol and a method of clocking the data. In addition, some serial buses require special waveforms and control signals. The Model 2108 provides the resources in a programmable format to meet the physical and logical characteristics of most interfaces.

# 1.1.1 Serial Bus Electrical Characteristics

The data bit is the very building block of any serial transmission and assumes physical properties that must be defined to suit a particular protocol. The Model 2108 provides the following programmable resources to define the serial bus electrical characteristics:

- A) Signal Type- differential, bi-polar or trinary

- B) Voltage Levels various levels from ECL, LVDS, TTL, +/-15Vdc, etc.

- C) Slew Rate min. 0.15V/ns to a max. 3V/ns

- D) **Termination** may be programmed on or off

The Model 2108 transmitter enables the user to set not only the default electrical characteristics of the bit, but also a second set which may be used to create "error" states.

# 1.1.2 Data Clocking

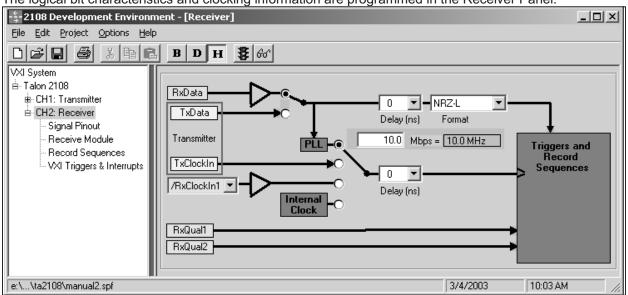

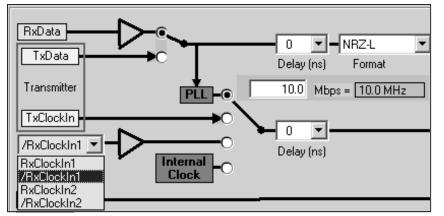

The Model 2108 provides internal clock sources for each channel which supports data rates from 2Kbps to 200Mbps. Additionally, the user may also select to clock the channels from external sources at the 2Kbps to 200Mbps rates. In addition the 2108RX receiver may be phase locked to the external clock or to the received data.

# 1.1.3 Waveform Data

Some serial buses require data which cannot be generated using logical ones and zeros to be output as part of a data stream. This data is usually referred to as "invalid bit format". The Model 2108TX transmitter provides register space to define up to eight waveforms. Four can be inserted in serial data streams and four are used to generate word or frame gaps. The 2108RX receiver's trigger logic may be programmed to recognize and trigger on waveform data as well.

# 1.1.4 Control Signals

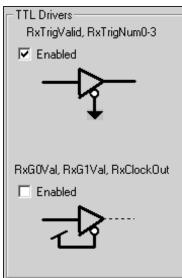

In addition to clock and data signals some serial buses require separate signals for sync, enables and triggering. The Model 2108 provides additional signals for emulating complex serial interfaces or to synchronize with other instruments in the test system. These signals are:

| Markers (2)      | Output from the Model 2108TX, these signals may be programmed aligned or 1 to 3 bit times prior to or following the first and last data bits of a word or frame.                                                                  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output Flags (2) | Output from the Model 2108TX, these signals are pulses and can be used to trigger the UUT or other instruments in the test system. They are aligned to the first bit of a word or frame and remain true until the word is output. |

| Strobe (1)       | Output from the Model 2108TX, this signal can be used to sync to the data bits or as a clock in bi-phase format applications.                                                                                                     |

| Sync Pulse (1)   | Output from the Model 2108TX, this signal may be programmed to start at a bit and remain true for up to 16 bits.                                                                                                                  |

| Input Flags (2)  | Input to the Model 2108TX, these signals may be used to start execution of a data stream or word from the Model 2108TX Transmitter.                                                                                               |

| Trigger Data (5) | Signals routed from the 2108RX to the adjacent 2108TX as well as the front panel, used to start execution of a unique data table and monitor receiver status.                                                                     |

| Qualifiers (2)   | Input to the Model 2108RX, tests for High or Low to trigger recording.                                                                                                                                                            |

# 2 Installation

The following sections describe the hardware and software installation procedure for the 2108. Refer to the "2108 Reference Manual" for module installation and jumper/termination options.

# 2.1 Hardware Installation

The following sections discuss the installation procedure for the 2108 system.

WARNING Use ESD protocols whenever handling the 2108 or any of its modules.

### 2.1.1 Receiving Inspection

Check the shipment at the time of delivery and inspect each box for damage. Describe any box damage and list any shortages on the delivery invoice.

1. **Unpack the boxes.** Unpack the boxes in a clean and dry environment. Save all the packing material in case the instrument must be returned for service.

In addition to the 2108 system, the following items are shipped with each unit:

- 2108 Operators Manual

- 2108 Reference Manual

- 2108 Interconnect Reference Manual

- 2108 Configuration Sheet

- 2108 System CD (Includes 2108 VXIplug&play Instrument Driver, 2108 Development System and electronic copies of the manuals in PDF format.).

- Check for damage. Inspect the equipment carefully for any signs of physical damage regardless of the condition of the shipping boxes. In the case of physical damage, call the shipper immediately and start the claim process. Call the Customer Service representative (800-722-2528) to inform them that the shipment arrived damaged. Please be prepared to provide a detailed damage report.

### 2.1.2 Returning Equipment

Follow these steps when you return equipment to Talon:

- 1. **Save the packing material.** Always return equipment in its original packing material and boxes. If you use inadequate material, you'll be responsible for any shipping damage repair as carriers won't accept responsibility on incorrectly packed equipment.

- 2. **Call Customer Service and ask for a return authorization.** The Customer Service representative (800-722-2528) will ask for your name, telephone number, company name, equipment type, model number, serial number, and a description of your problem.

- 3. Pack and ship the equipment to:

Talon Instruments 4 Goodyear Irvine, CA 92618

# 2.1.3 Preparation for Storage

The 2108 should be stored in a clean, dry environment. In high humidity environments, protect the 2108 from temperature variations that could cause internal condensation. The following environmental conditions apply to both shipping and storage:

| Temperature       | -40°C to +70°C                 |

|-------------------|--------------------------------|

| Relative Humidity | Not controlled, non-condensing |

| Altitude          | <40000 ft. (12192 m)           |

| Vibration         | <2g                            |

| Shock             | <40g                           |

### 2.1.4 Preparation for Use

Prior to installing the 2108 module in the VXI chassis, several settings can be made via two switches located on the 2108 baseboard.

Figure 2-3 2108 Baseboard Rev NC Switch Settings

The baseboard revision is located on the back side etched in copper.

The following sections covers the following topics:

- Logical Address Selection

- VXI Interrupt Level Selection

- A24/A32 Map Selection

# 2.1.4.1 Logical Address Selection

The VXI chassis Resource Manager identifies units in the system by the unit's logical address.

The logical address of the 2108 can be statically or dynamically configured. An eight position DIP switch located on the baseboard, see figure 2-1, is used to assign the logical address. A logical address setting of 255 (all positions down, factory default) will enable the dynamic addressing mode. The logical address for each channel will be assigned by the resource manager. Logical address zero is reserved for the slot 0 controller and is invalid. Any other logical address setting will cause the 2108 to request four consecutive logical addresses starting with the address coded on logical address switch. The logical address setting must be a multiple of 4, the lower two logical address bits are ignored.

|     |     |     | Logical Add | Iress Switch | 1   |     |     |

|-----|-----|-----|-------------|--------------|-----|-----|-----|

| 8   | 7   | 6   | 5           | 4            | 3   | 2   | 1   |

| LA7 | LA6 | LA5 | LA4         | LA3          | LA2 | LA1 | LA0 |

Switch position 1 through 8 corresponds to bits 0 through 7 of the logical address. The "ON" setting sets the corresponding bit of the logical address to a one (1).

Channel one of each 2108 baseboard will be mapped to the lowest logical address assigned and channel four will be mapped to the highest.

The figures above shows an example where the logical address is set to 24 (position 5 and 4 down). This will cause the following logical address mapping:

- Channel 1: LA24 (logical address 24)

- Channel 2: LA25

- Channel 3: LA26

- Channel 4: LA27

The 2108 baseboard will be assigned four logical addresses even if less than four modules are installed.

### 2.1.4.2 VXI Interrupt Selection

The first three switch positions of Interrupt/Map switch are used to assign the VXI interrupt level. A value of zero disables VXI interrupt generation by the 2108. Values between one and seven select the interrupt of the same value, i.e., if position 2 and 3 are on and position one is off then VXI interrupt level 6 will be used by the 2108.

Factory default: VXI interrupts disabled.

|                 |               | Interrupt/N     | lap Switch |                                                                                                   |                 |             |

|-----------------|---------------|-----------------|------------|---------------------------------------------------------------------------------------------------|-----------------|-------------|

| 8 7 6 5 4 3 2 1 |               |                 |            |                                                                                                   |                 |             |

| Reserved        |               | Map             | ping       |                                                                                                   | Interrupt Level |             |

|                 | 7<br>Reserved | 7 6<br>Reserved | 7 6 5      | Interrupt/Map Switch           7         6         5         4           Reserved         Mapping | 7 6 5 4 3       | 7 6 5 4 3 2 |

| Position 3 | Position 2 | Position 1 | VXI Interrupt Level                  |

|------------|------------|------------|--------------------------------------|

| OFF        | OFF        | OFF        | Disabled (none)                      |

| OFF        | OFF        | ON         | Level One Selected (factory default) |

| OFF        | ON         | OFF        | Level Two Selected                   |

| OFF        | ON         | ON         | Level Three Selected                 |

| ON         | OFF        | OFF        | Level Four Selected                  |

| ON         | OFF        | ON         | Level Five Selected                  |

| ON         | ON         | OFF        | Level Six Selected                   |

| ON         | ON         | ON         | Level Seven Selected                 |

### 2.1.4.3 A24/A32 Map Selection

The memory space each 2108 channel will request can be set to either A24 (position 4 up) or to A32 (position 4 down).

The size of the A24/A32 memory requested can be set to either 4M (position 5 up) or 2M (position 5 down). Empty channel slots will not request any A24/A32 memory.

Factory Default: A32 memory selected, 4M map size.

|   |            |          | Interrupt/I | Map Switch                                |                 |            |   |

|---|------------|----------|-------------|-------------------------------------------|-----------------|------------|---|

| 8 | 7          | 6        | 5           | 4                                         | 3               | 2          | 1 |

|   | Reserved   |          | 4M/2M       | A24/A32                                   |                 | Interrupts |   |

|   |            |          |             |                                           |                 |            |   |

|   | Position 5 | Position | 4           | Regist                                    | er Mapping      |            |   |

|   | OFF OFF    |          |             | A32 4M Register Mapping (factory default) |                 |            |   |

|   | OFF ON     |          |             | A24 4M Register Mapping                   |                 |            |   |

|   | ON OFF     |          |             | A32 2M Register Mapping (factory default) |                 |            |   |

|   | ON         | ON       |             | A24 2M R                                  | egister Mapping |            |   |

|   |            |          |             |                                           |                 |            |   |

# ATTENTION GPIB-VXI slot zero controllers do not support A32 register transfers. A24 register mapping must be selected for 2108 operation with these controllers.

### 2.1.5 Installation

The 2108 must be installed in a VXI mainframe in any slot except slot 0 (zero), which is reserved for the Resource Manager. Always check P1 and P2 for bent pins prior to installation. When inserting the 2108

into the mainframe, it should be gently rocked back and forth to seat the connectors into the backplane receptacles.

### 2.1.5.1 Initial Power-On

With the 2108 properly installed in a VXI chassis, turn on the external power supplies, if required, followed by the chassis power. Refer to the appropriate interconnect module reference manual for external power requirements.

# 2.2 Software Installation

The 2108 is shipped with a VXI Plug&Play Instrument Driver as well as the 2108 Project Development System. Both pieces of software are included on the CD shipped with the 2108 system. In addition to the software, the CD also contains all the operator and reference manuals for the 2108 in PDF format.

### 2.2.1 VXI Plug&Play Instrument Driver

The 2108 Instrument Driver links the communication interface and an application development environment. It provides a higher level, more abstract view of the instrument. It also provides ADE-specific information that supports the capabilities of the ADE, such as a graphical representation.

Some of the ADEs that this Instrument Drivers supports are listed below:

- Borland Turbo C/C++

- Agilent Technologies Agilent VEE

- Microsoft Visual Basic

- Microsoft Visual C/C++

- National Instruments LabVIEW

- National Instruments LabWindows/CVI

Included with the Instrument Driver is the Soft Front Panel. The soft front panel is a graphical user interface for the 2108. It is used to verify communications and functionality when the 2108 is first integrated into the system.

The 2108 VXI Plug&Play Instrument Driver requires that VISA be installed. Contact your Slot 0 Resource Manager manufacturer.

To install 2108 Plug&Play Instrument Driver:

1. Insert the 2108 System CD into your computer's CD-ROM drive. The 2108 System Installation menu will run automatically. If the installation menu, figure 2-4, does not appear, run setup.exe from the CD root directory.

Figure 2-4 2108 System CD Installation Menu

- 2. Press the "Install Instrument Driver" command button.

- 3. The installer will remove any versions that are currently loaded on the computer.

- 4. If a previous version was removed in step 3, then repeat step 2.

- 5. Follow the installer directions.

- 6. After the Instrument Driver is installed, the 2108 Soft Front Panel will be launched.

The following files are installed from the CD:

- ANSI C source code for the Instrument Driver and Soft Front Panel, i.e., .c, .h files.

- MS Windows 32 bit DLL library, i.e., ta2108\_32.dll, ta2108.def files.

- Microsoft 32 bit DLL import library, i.e., ta2108.lib file.

- Function panel file, i.e., .fp file.

- MS Visual Basic Function Declaration text file, i.e., .bas file.

- Windows help file (.hlp file).

Visit the Talon Instruments web site at "www.taloninst.com" and check for 2108 Instrument Driver updates.

# 2.2.2 2108 Project Development System (PDS)

The 2108 PDS is a comprehensive application package that provides the user with easy to use graphical programming tools to develop set-up files, execute tests and view the recorded data. The package contains 3 distinct application programs to provide the majority of users with all the necessary functions to develop a functioning serial interface. It was developed for the Windows environment and operates on Win95, 98, 2000, or NT based systems.

# 2.2.2.1 Project Development Editor (PDE)

The Project Development Editor is the basic application program. It provides the resources to program the logical and physical characteristics of a serial interface. In addition it provides the tools to program data tables and test sequences for stimulating the Unit Under Test, (UUT). Record triggers based on unique start patterns are also easily programmed using the 2108RX receiver's GUIs. Files created by the PDE are saved and may be downloaded using the VXI drivers or the Execution Manager.

# 2.2.2.2 Execution Manager (EM)

The Execution Manager application provides an interactive link to download set-up files from the VXI controller to a Model 2108. In addition it allows the user to select and run any test sequences defined using the PDE. The user may loop from 1 to 32k times or run in continuous mode to aid in program debugging. 2108RX receivers may be "ARMED" using the EM.

# 2.2.2.3 Serial Logic Analyzer (SLA)

The Serial Logic Analyzer application provides an interactive means of uploading recorded data from the 2108RX receiver. The data may be viewed as "raw" data or segmented by bit count, labeled and displayed as binary, hex, decimal or ASCII. This decoded data display is accomplished by defining templates that may be saved as a file. The template file may be applied to interactively recorded data when using the Execution Manager or used to analyze data recorded over a period of time. The SLA also provides search functions which operate on raw or decoded data or the label.

### NOTE

Under Windows NT4, this software requires that Service Pack 2 or later be installed. Otherwise, the digital signals in the Timing and Table Editors may not display correctly.

To install 2108 Project Development System:

- 1. Remove any older versions of the Development System through the "Start->Settings->Control Panel->Add/Remove Programs".

- 2. Insert the 2108 System CD into your computer's CD-ROM drive. The 2108 System Installation menu will run automatically. If the installation menu does not appear run setup.exe from the CD root directory.

- 3. Press the "Install Development System" command button.

- 4. Follow the installer directions.

Visit the Talon Instruments web site at "www.taloninst.com" and check for 2108 Development System updates.

# 3 2108 Front Panel

The 2108 front panel provides the hardware interface to the UUT. Figure 3-1 illustrates the front panel and its connectors:

Figure 3-1 2108 Front Panel

The 2108 is a modular system that can hold up to four transmit or receive channels. Each transmit/receive channel connects to the UUT/ITA via the interconnect module. Refer to the specific interconnect module reference manual for detailed front panel description.

# 3.1 LED Indicators

The following sections describes the LED indicator for the transmitter and receiver interconnect modules.

### 3.1.1 Transmitter Interconnect LED Indicator

The transmitter interconnect module LED is used to indicate the operating status of the transmitter as well as the driver status. The color codes are:

| OFF   | The transmitter is outputting "Idle" or "Standby" CMT.                                  |

|-------|-----------------------------------------------------------------------------------------|

| GREEN | The transmitter is outputting a user defined CMT.                                       |

| RED   | The drivers have shut down due to either an over current or over temperature condition. |

### 3.1.2 Receiver Interconnect LED Indicator

The receiver interconnect module LED is used to indicate the operating status of the receiver. The color codes are:

| AMBER | The receiver is currently waiting for a trigger (ARMed). |

|-------|----------------------------------------------------------|

| GREEN | The receiver is currently recording post trigger data.   |

# 3.2 SMA Connector

The SMA is used to input a single ended ECL clock (TxCLKIN1 or RxCLKIN1).

# 3.3 Power Connector

The transmitter power connector is used to provide the V+ and V- supply voltages to the programmable drivers.

Table 3-1 below lists the pinouts of the TX01 Power connector.

| Pin Number | Signal |

|------------|--------|

| A          | V+     |

| В          | GND    |

| С          | V-     |

| D          | GND    |

Table 3-1 Power Connector Pinouts

Figure 3-2 Power Connector

# 3.4 J1-J4 I/O Connector

The front panel I/O connector is used to connect the 2108 signals to the UUT/ITA fixture.

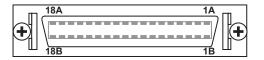

Figure 3-3 J1-J4 Connector

| Pin Number                    | Trar   | smitter        | Rec    | eiver          |

|-------------------------------|--------|----------------|--------|----------------|

|                               | Signal | Default Source | Signal | Default Source |

| 2A                            | TxSig1 | TxData         | RxI    | Data+          |

| 4A                            | TxSig2 | TxClkOut       | RxI    | Data-          |

| 6A                            | TxSig3 | TxMarker1      | RxC    | lkin2+         |

| 8A                            | TxSig4 | TxMarker2      | RxC    | Cikin2-        |

| 10A                           | TxSig5 | TxFlagOut1     | RxG    | Qual1+         |

| 12A                           | TxSig6 | TxFlagOut2     | RxC    | Qual1-         |

| 14A                           | TxSig7 | TxSyncPulse    | RxC    | Qual2+         |

| 16A                           | TxSig8 | TxBusy         | RxC    | Qual2-         |

| 18A                           |        | NU             | RxSig1 | RxArm          |

| 2B                            | Tx     | FlagIn1        | RxTr   | igValid        |

| 4B                            | Тx     | FlagIn2        | RxTri  | igNum0         |

| 6B                            | Tx     | Clkln2+        | RxTri  | igNum1         |

| 8B                            | T×     | :Clkln2-       | RxTri  | igNum2         |

| 10B                           | Т      | xBusy          | RxTri  | igNum3         |

| 12B                           | TxS    | yncPulse       | Rx(    | G0Val          |

| 14B                           |        | NU             | Rx(    | G1 Val         |

| 16B                           |        | NU             | RxC    | OlkOut         |

| 18B                           |        | NU             | RxSig2 | RxBusy         |

| All other pins signal ground. |        | ·              |        |                |

Table 3-3 lists the I/O channels assigned to J1-J4 for both the transmitter and receiver.

Table 3-3 J1-J4 I/O Connector Assignments

# 3.5 2108 Front Panel Mating Connectors

The following table lists the manufacturer part number and Talon order number for the front panel mating connectors.

Table 3-2 lists the manufacturers part numbers and Talons part numbers for the 2108 mating connectors.

| Connector | Manufacturer Part Number                 | Talon Order Number |

|-----------|------------------------------------------|--------------------|

| J1-J4     | AMP P/N "2-178238-5"                     | 21 08/300          |

| Power     | Positronix Industries P/N "SGM4FSCT0000" | 21 08/304          |

| Table 3-2 Mating | Connector | Part Numbers |

|------------------|-----------|--------------|

|------------------|-----------|--------------|

# 4 Operation

The steps required to create a test program using the 2108 are very similar to those required to use any other VXI module. Regardless of the user's choice of programming path - whether it is the plug&play instrument driver, Development Editor, A24/A32 register-based access or a combination of these - the following basic steps will apply:

- 1. INITIALIZE the VXI session for each 2108 channel.

- 2. CONFIGURE the 2108 settings and structures for the application.

- 3. Enable, or SOURCE, the output drivers.

- 4. Issue the EXECUTE commands.

- 5. Utilize STATUS and POST PROCESS functions to evaluate/analyze results.

- 6. CLOSE the VXI session.

The following sections describes each step in more detail with respect to the Development Editor and VXI plug&play instrument driver function(s).

Programming the 2108 using the Development System is described in the "2108 Development System Users Manual".

# 4.1 Initializing the VXI Session

Each channel of a 2108 module has a unique logical address and requires its own session handle.

If a project file is used to configure the 2108 channels then the "*ta2108\_LoadProject*" function will initialize all the channels automatically by calling the "*ta2108\_autoConnectToAll*" function. The session handle of any channel initialized by the "*ta2108\_LoadProject*" function can be queried by first selecting the channel using the "*ta2108\_Select*" function and then calling the "*ta2108\_GetConfig*" function.

If VXI plug&play functions are used to configure the 2108 channels then any of the following functions can be used to open a session:

- 1. "ta2108\_init"

- 2. "ta2108\_autoConnectToFirst"

- 3. "ta2108\_autoConnectToLA"

- 4. "ta2108\_autoConnectToSlot"

- 5. "ta2108\_autoConnectToAll"

# 4.2 Configure the 2108 Settings and Structures

Talon recommends using the Project Development Editor (PDE) to configure the 2108 channels. The PDE provides a graphical representation of the 2108 hardware resources.

The following sections describes the process for configuring the 2108 channels using the PDE. The corresponding VXI plug&play functions required to perform the same action will be listed as well.

### 4.2.1 Defining the 2108 PDE Configuration

The first step in using the PDE is to configure the 2108 (s) being programmed by defining the number and type of instruments installed in each channel slot.

When started the PDE will load the last file that was last saved. To create a new project select the "File->New" command. The PDE will create a new project with one 2108 module that contains one transmitter channel and one receiver channel.

To delete a 2108 Module from the project, right click on the "**Talon 2108**" and select "**Delete 2108 Module**" command.

To add a 2108 Module, right click on "VXI System" in the menu directory and select "Add...", "2108 Module".

To add a transmit or receive channel, right click on the Talon 2108 module and select "**Add...**". Select the hardware and channel position. A configuration sheet is shipped with all Talon 2108 Modules that identifies the installed hardware.

| -5-2108   | Development Environment |                    |            |

|-----------|-------------------------|--------------------|------------|

| File Edit | : Project Options Help  |                    |            |

| DØ        | B S X B B B             | <b>D H 💲</b> боʻ   |            |

| VXI Syste |                         |                    |            |

|           | Add >                   | CMT Table          |            |

|           | Сору                    | Test Sequence      |            |

|           | Paste                   | Transmit Channel 🔸 | CH1        |

|           | Delete 2108 Module      | Receive Channel 🔸  | CH2        |

|           | Rename Ctrl+R           | 2108 Module        | CH3<br>CH4 |

|           |                         |                    |            |

This step defines the installed hardware for the PDE and does not have any corresponding VXI plug&play functions.

# 4.2.2 Configure the 2108 Transmitter

The 2108TX module provides the necessary resources to output data in a serial stream using different formats, protocols, data rates, etc. It also provides auxiliary signals such as a shared clock, markers, sync, triggers, etc., required by many serial interfaces.

The operation of the 2108TX requires the user to define the characteristics of the serial interface to be emulated. This includes data to be output and the sequence in which the user wants the data output.

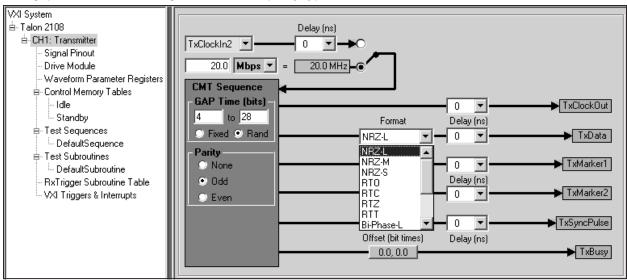

# 4.2.2.1 Logical Bit Settings

The logical bit characteristics are programmed using the Transmitter Panel shown below.

| -\$-2108 Development Environment -               | [Transmitter]                       | - 🗆 🗵         |

|--------------------------------------------------|-------------------------------------|---------------|

| Eile Edit Project Options Help                   |                                     |               |

| DE B S A R B B                                   | D H \$ 60                           |               |

| VXI System                                       |                                     |               |

| ia⊢Talon 2108                                    | Delay (ns)                          |               |

| ia⊢CH1: Transmitter                              | TxClockIn2 ▼ 0 ▼ ->->               |               |

| - Signal Pinout                                  |                                     |               |

| - Drive Module<br>- Waveform Parameter Registers | 10.0 Mbps = 10.0 MHz                |               |

| Control Memory Tables                            | CMT Sequence                        |               |

|                                                  | GAP Time (bits) -                   | TxClockOut    |

| Standby                                          | 16 Format Delay (ns)                |               |

| ⊨ Test Sequences                                 | ● Fixed ● Rand                      | → TxData      |

| DefaultSequence                                  | Parity                              | ·             |

| ia Test Subroutines                              | ● None 0.0, 0.0 0 ▼                 | TxMarker1     |

| - RxTrigger Subroutine Table                     | O Odd Offset (bit times) Delay (ns) |               |

| VXI Triggers & Interrupts                        | 0.0, 0.0                            | ► TxMarker2   |

|                                                  |                                     |               |

|                                                  |                                     | ► TxSyncPulse |

|                                                  | Offset (bit times) Delay (ns)       |               |

|                                                  | 0.0, 0.0                            | TxBusy        |

|                                                  |                                     |               |

| <u> </u>                                         |                                     |               |

| e:\\ta2108\manual2.spf                           | 3/4/2003 10:06                      | AM ///        |

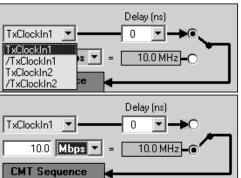

In the Transmitter Panel the user programs:

# **Clock Source** External or internal clock sources may be selected as the transmitter master clock.

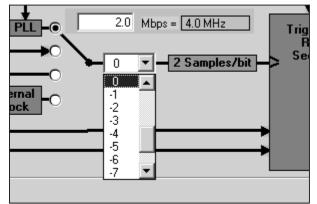

Bit Rate B

Bit rates from 2kBps to 200MBps may be entered.

|    | 10.0   | Mbps 💌 | = | 10.0 MHz |

|----|--------|--------|---|----------|

| CM | IT Sec | Mbps   |   |          |

|    |        | Kbps   |   |          |

**Bit Formats** The required bit format may be selected from a pull down selector.

Parity

Parity if required is set as None, Odd or Even.

| - Parity |  |

|----------|--|

| None     |  |

| 💭 Odd    |  |

| 💭 Even   |  |

Gap

Gap times may be set to fixed or random with limits from 4 to 65k bit times.

| GAP Time (bits) — | - GAP 1 | lime (bits) – |

|-------------------|---------|---------------|

| 16                | 16      | to 3000       |

| 🖲 Fixed 🔘 Rand    | 🔘 Fixe  | ed 💿 Rand     |

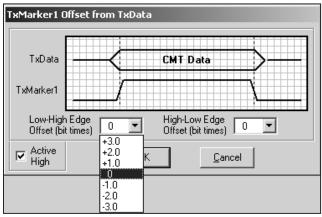

Marker(s) May be set to operate coincident with the data or +/- 3 clocks from the active data and active high or low.

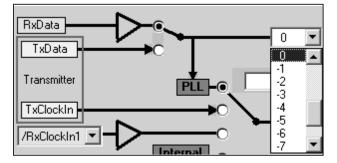

Delay

Delays in 1ns increments from +/- 10ns may be programmed to most signals when cable or UUT delays cause synchronization problems.

VXI plug&play functions for logical bit programming:

ta2108\_txSetSignalParameters ta2108\_txSetSignalOffset

ta2108\_txSetSignalDelay

ta2108\_txSetGapMinMax

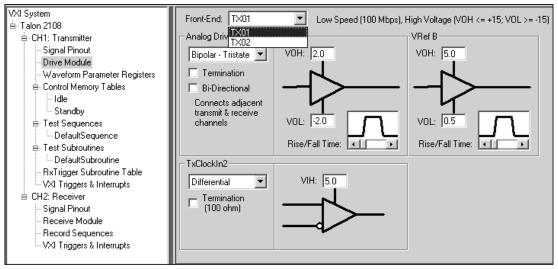

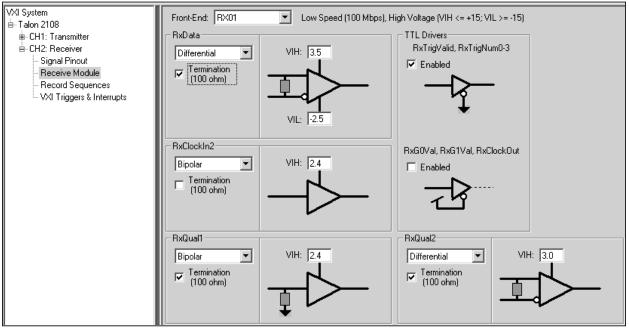

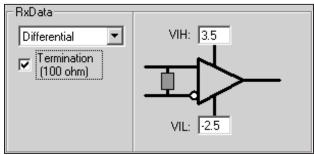

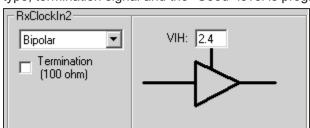

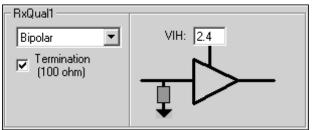

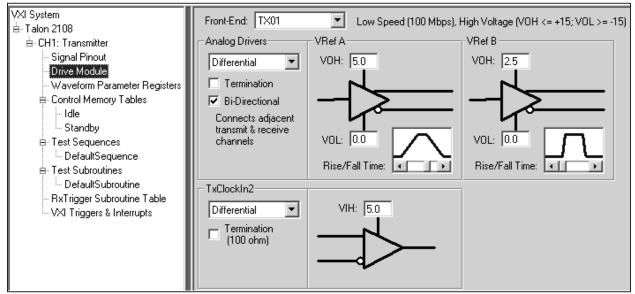

# 4.2.2.2 Electrical Characteristics

The electrical bit characteristics are programmed in the Drive Module Panel shown below. The front end interconnect type is also specified on this panel.

The bit characteristics to be programmed are:

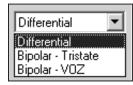

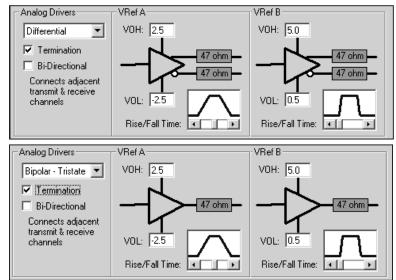

**Signal Type** The selections for most I/O modules include Differential, bi-polar with tri-state or bi-polar with a third state (trinary).

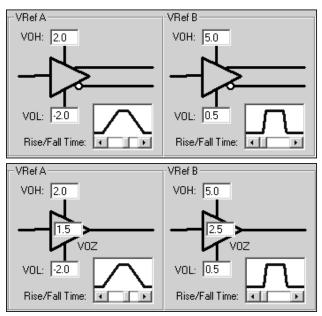

#### **Signal Voltage**

VrefA is the primary voltage reference requiring the output levels VOH and VOL to be entered, (3rd voltage if Bi-polar VOZ is selected), slew rate is selected by use of the slide bar window (Rise/Fall Time); VRefB may be used as a secondary voltage reference to generate errors or as a margining voltage reference

#### **Termination**

Most of the I/O modules allow the selection of terminated or un-terminated signals.

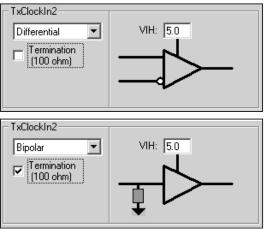

# **TxClockIn2**If using external clock 2 as Clock Source the "signal good" level is programmed<br/>in this window for differential or bi-polar along with the termination choice.

# **Bi-directional** If selected the transmitter I/O module will be the only connection to the interface bus and incoming data will be routed to the adjacent 2108RX module for bi-directional operations.

VXI plug&play functions for electrical bit characteristics:

ta2108\_txSetFrontEndControl

ta2108\_txSetFrontEndInput

ta2108\_txSetDriverReference

# 4.2.2.3 Signal Routing

The 2108TX has multiple signals which may or may not be needed for the serial interface being programmed.

| VXI System                                              | Pin | Connector   | Assigned Signal | UUT Signal | Description                                                 |

|---------------------------------------------------------|-----|-------------|-----------------|------------|-------------------------------------------------------------|

| ia⊡ Talon 2108                                          | 2A  | TxSig1      | TxData          | -          | <output dynamic="" error="" reference="" with=""></output>  |

| Ė-CH1: Transmitter                                      | 4A  | TxSig2      | /TxData         | -          | <output dynamic="" error="" reference="" with=""></output>  |

| - Signal Pinout                                         | 6A  | TxSig3      | TxMarker1       | -          | <static enable="" output=""></static>                       |

| Drive Module<br>Waveform Parameter Registers            | 8A  | TxSig4      | TxMarker2       | -          | <static enable="" output=""></static>                       |

| B- Control Memory Tables                                | 10A | TxSig5      | TxFlagOut1      | -          | <static enable="" output=""></static>                       |

|                                                         | 12A | TxSig6      | TxFlagOut2      | -          | <static enable="" output=""></static>                       |

| - Standby                                               | 14A | TxSig7      | TxSyncPulse     | -          | <static enable="" output=""></static>                       |

| ⊨-Test Sequences                                        | 16A | TxSig8      | TxBusy          | -          | <static enable="" output=""></static>                       |

| DefaultSequence                                         | 2B  | TxFlagIn1   |                 | -          | <ttl 1="" flag="" input=""></ttl>                           |

| ia⊢Test Subroutines                                     | 4B  | TxFlagIn2   |                 | -          | <ttl 2="" flag="" input=""></ttl>                           |

| DefaultSubroutine                                       | 6B  | TxClockIn2+ |                 |            | <programmable clock="" input="" positive=""></programmable> |

| RxTrigger Subroutine Table<br>VXI Triggers & Interrupts | 8B  | TxClockIn2- |                 | -          | <programmable clock="" input="" negative=""></programmable> |

|                                                         | 10B | TxBusy      |                 |            | <ttl busy="" output="" transmitter=""></ttl>                |

| - Signal Pinout                                         | 12B | TxSyncPulse |                 | -          | <ttl pulse="" sync="" transmitter=""></ttl>                 |

| - Receive Module                                        | SMA | TxClockIn1  |                 |            | <high clock="" ecl="" input="" speed=""></high>             |

The TxData and TxClockOut signals are always output on pins 2A and 4A if bi-polar mode is selected. If differential is selected then TxData will be on pin 2A and /TxData will be on pin 4A. Grounds will always be on the odd pins between signals.

The user selects the signals needed and routes them to the selected pins using the pulldown selections in the Assigned Signals column. The user may also elect to enter names in the UUT and Description columns for documentation purposes.

VXI plug&play functions for signal routing:

#### ta2108\_txSetUserSignal

### 4.2.2.4 Waveform Definition

Some buses use non-logical bit patterns for sync codes or data. For example, the military 1553 bus has a command word sync code which is a signal represented as  $1\frac{1}{2}$  bit times high followed by  $1\frac{1}{2}$  bit times low. Another example is a pulse stream where 2 bits low out of 8 is a zero and 6 bits low out of 8 is a one. These waveforms can be programmed via the Waveform Parameters Register panel.

There are two types of waveform registers:

**Waveforms** Four custom waveforms (WPR0, WPR1, WPR3 & WPR4) may be defined as using Voltage Reference A or B, the number of bit times (4 to 12 bits), and the waveform. Waveforms are programmed by selecting a cell and clicking or entering an L or H to set desired state, (bi-phase selections allow ½ bit time selections between 2 & 12 bits).

|         | Vref      | #Bits      | 1 2 | 3 4           | 5 6 | 5 7 | 8 9           | 10 11 | 12 |   |   |   |    |

|---------|-----------|------------|-----|---------------|-----|-----|---------------|-------|----|---|---|---|----|

| WPR0    | A         | 4          |     |               |     |     |               |       |    |   |   |   |    |

| WPB1    | Α         | 8          |     |               |     |     |               |       |    |   |   |   |    |

| WPR2    | Α         | 8          |     |               |     |     |               |       |    |   |   |   |    |

| WPR3    | A         | 12         |     |               |     | -   |               |       |    |   |   |   |    |

| 1 1110  |           | 14         |     | $\rightarrow$ |     |     | $\rightarrow$ |       |    |   |   |   |    |

| I WI HS |           |            |     |               |     |     |               |       |    |   |   |   |    |

| WINS    | Vref      | #Bits      |     | 2             | 3   | 4   |               | 5     | 6  | 7 | 8 | 9 | 10 |

| WPR0    |           |            |     | 2             | 3   | 4   |               | 5     | 6  | 7 | 8 | 9 | 10 |

|         | Vref      | #Bits      |     | 2             | 3   | 4   |               | 5     | 6  | 7 | 8 | 9 | 10 |

| WPR0    | Vref<br>A | #Bits<br>3 |     |               | 3   | 4   |               | 5     | 6  | 7 | 8 | 9 | 10 |

#### Gap Waveforms

There are four waveforms that may be used as Gap waveforms, (GRP0, GPR1, GPR2 & GPR3). They are represented as a single bit time and are programmed by selecting the Voltage Ref. A or B and the desired state, High, Low or Tri-state. Bi-phase selections allow for ½ bit time selections.

| GPR0         | A    | 1                |                      |

|--------------|------|------------------|----------------------|

| GPR1         | Α    | 1                |                      |

| GPR2         | Α    | 1                |                      |

| GPR3         | Α    | 1                |                      |

|              |      |                  |                      |

|              |      |                  |                      |

| GPR0         | Α    | 1                |                      |

| GPR0<br>GPR1 | A    | 1                |                      |

|              |      | 1<br>1<br>1      |                      |

| GPR1         | A    | 1<br>1<br>1      | =                    |

|              | GPR1 | GPR1 A<br>GPR2 A | GPR1 A 1<br>GPR2 A 1 |

VXI plug&play functions for waveform definition:

### ta2108\_txSetWaveformRegisters

#### 4.2.2.5 Define the Bit Sequence(s)

All serial interfaces pack the bits in some logical sequence such that the receiving device can reverse the sequence and extract meaningful data from the data stream. The schemes to logically pack data into "frames" or "packets" is unique for every interface. The 2108TX allows the programming of almost any conceivable combination of bit sequences, thereby allowing the emulation of interfaces with unique start/stop codes, parity bits, bit stuffing, as well as the generation of continuous data.

#### 4.2.2.5.1 Control Memory Tables

The programming of bit sequences is accomplished in the Control Memory Table panel. This panel represents the 8Mbits of memory reserved for data to be transmitted by the 2108TX. Frames are defined as tables. A table may be just a data word or comprised of multiple data word(s), waveform(s), gaps or

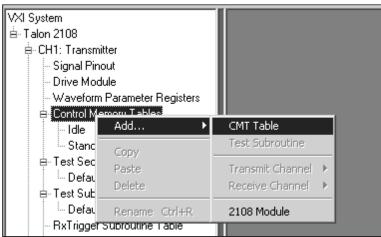

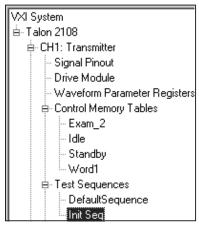

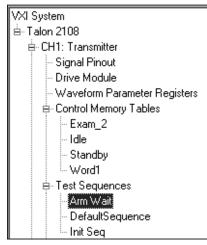

random data words. New tables may be added by right clicking on Control Memory Tables in the menu directory, selecting Add CMT Table and entering a name for the table.

VXI plug&play functions for defining a CMT:

### ta2108\_txDefineCMT

### 4.2.2.5.2 Programming Control Memory Tables

A Control Memory Table is programmed by double clicking on the table name and entering or selecting the elements which define the table characteristics. The following entries are available:

| Table | e size: | 1  | Bit Order: LS | iB 💌 Paritj | y Control: | Reset | Parity | r Def | ault Bank: / |  |

|-------|---------|----|---------------|-------------|------------|-------|--------|-------|--------------|--|

|       | M1      | M2 | Туре          | Waveform    | #Bits      | Data  |        | AP    | Description  |  |

| 1     | L       | L  | Data          |             | 8          |       | 0x00   |       |              |  |

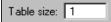

Table Size

Enter the number of steps or words needed for the data. Any number up to the available memory depth may be entered.

**Bit Order** Select from the pull down window to select the order in which the data is transmitted, Most Significant Bit or Least Significant Bit.

| _          |            |  |

|------------|------------|--|

| Bit Order: | LSB        |  |

| Туре       | LSB<br>MSB |  |

| Diata      | MOD        |  |

Parity Control

Provides selections for the user to Reset the parity calculator, Resume to continue the parity calculation from a previous table, or Disable the parity calculation altogether.

| Parity Con | itrol: Reset 💽                               |

|------------|----------------------------------------------|

| Reset      | Clear parity count when this table starts    |

| Resume     | Continue parity count from previous table    |

| Disable    | Do not change parity count during this table |

**Parity** This window allows the user to select or override the default parity programmed in the Transmitter Panel.

| Parity: Default 💌 |                                    |  |  |  |  |

|-------------------|------------------------------------|--|--|--|--|

| Default           | Use Transmitter parity setting     |  |  |  |  |

| Invert            | Use opposite of Transmitter parity |  |  |  |  |

| None              | No parity for this table           |  |  |  |  |

| Odd               | Odd parity for this table          |  |  |  |  |

| Even              | Even parity for this table         |  |  |  |  |

Bank

The 8Mbits of memory is divided into two 4Mbit banks for ping-pong operations, the pull-down selector is used to select the bank A or B to store the table being defined.

M1 or M2 If the Marker signals are to be used while the step data is transmitted the level is selected as low (L) or high (H) for M1 and/or M2.

|   | M1  | M2 |

|---|-----|----|

| 1 | L 🖵 | L  |

|   | L   |    |

|   | Н   |    |

Туре

The type of data to be output for each step of the table is selected in this pull-down window by clicking on one of the following choices:

| Туре     |                                                       |

|----------|-------------------------------------------------------|

| Data     | <b>*</b>                                              |

| Data     | User defined data (4 to 48 bits)                      |

| PRBS     | Pseudo Random Bit Sequence (4 to 65536 bit times)     |

| Gap      | User defined Inter-message Gap (4 to 65536 bit times) |

| TGap     | Transmitter Gap setting (Random: 4 to 65000 bits)     |

| Waveform | Special Waveform                                      |

| Data     | Fixed data from 4 bits to 48 bits in length.                                                    |

|----------|-------------------------------------------------------------------------------------------------|

| PRBS     | Pseudo random bit sequence from 4 to 65k bits.                                                  |

| Gap      | Fixed intermessage gap using one of the Gap Wave-<br>forms from 4 to 65k bit times.             |

| ТGар     | Uses the default Transmitter Panel setting (random or fixed) and one of the Gap waveforms.      |

| Waveform | One of the 4 waveforms defined in the Waveform Pa-<br>rameters Register panel will be selected. |

**Waveform** If Waveform, Gap or TGap was selected as the Type of data to be transmitted in a step this window will be active and allow the selection of one of the previously defined waveforms.

| Туре     | Waveform              | #Bits                        | Data | - | AP | Description |  |

|----------|-----------------------|------------------------------|------|---|----|-------------|--|

| Waveform | WPR0 💌                | ]                            |      |   |    |             |  |

|          | WPR0 VR               | WPR0 VRef: A, 4 bits,        |      |   |    |             |  |

|          | WPR1 VB               | <b>wPR1</b> VRef: A, 4 bits, |      |   |    |             |  |

|          | WPR2 VRef: A, 8 bits, |                              |      |   |    |             |  |

|          | WPR3 VR               | VRef: A, 12 bits,            |      |   |    |             |  |

| Туре | Wave                                                                | form                                  | #Bits | Data |

|------|---------------------------------------------------------------------|---------------------------------------|-------|------|

| Gap  | GPRO                                                                | -                                     | 4     |      |

|      | GPR0         VRef: A, 1 bit,           GPR1         VRef: A, 1 bit, |                                       |       |      |

|      | GPR2                                                                | <b>2</b> VRef: A, 1 bit, <sup>—</sup> |       |      |

|      | GPR3                                                                | VRef: A, 1 bit,                       |       |      |

#Bits

Allows the entry of the number of bits represented in a step:

Data

The number of bits is from 4 to 48 (words longer than 48 bits are entered in consecutive steps and will be output as a single stream).

| Туре | Waveform | #B                                                               | lits |

|------|----------|------------------------------------------------------------------|------|

| Data |          | 4                                                                | -    |

|      |          | 4<br>5<br>7<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17 |      |

PRBS

The number of bits is from 4 to 65,536 of random data.

| Туре | Waveform | #Bits |

|------|----------|-------|

| PRBS |          | 65525 |

Gap

The number of Gap periods is from 4 to 65,536 bit times.

| Туре | Waveform | #Bits |

|------|----------|-------|

| Gap  | GPRO     | 5000  |

|      |          |       |

Data

Fixed data is entered in this window as binary, decimal or hex. Binary data is specified by specifying a 'b' at the end of the data, e.g., "1010 0001b". Decimal data does not require special characters. Hexadecimal data is specified by a "0x" preceding the data, e.g., "0x1234".

Spaces are allowed anywhere when entering data.

Once data in entered it will be displayed based on the selected format.

| B D H  | BDH     | B D H |

|--------|---------|-------|

| Binary | Decimal | Hex   |

AP

Clicking on this selection box will append a parity bit to the data using the parity control selected for this table, (parity may be calculated across any number of words by selecting AP only on the last data step in the table).

VXI plug&play functions for editing a CMT:

ta2108\_txSelectCMTStep

# ta2108\_txInsertCMTStep ta2108\_txDeleteCMTStep

### 4.2.2.5.3 Examples of CMT's

The following sections illustrates two CMT examples.

### 4.2.2.5.3.1 Simple 16-Bit One-Word Table

In this example, the user needs to output a single 16 bit, one word table, using M1 high as a write enable signal, MSB as the bit transmission order and adding a parity bit to the data. This type of data table is easily programmed by following these steps:

- a) Right click on Control Memory Tables in the menu directory

- b) Enter a name for the table, (Word1 for this example)

- c) Leave 1 as the step size

- d) Select MSB for the Bit Order

- e) Select H for M1

- f) Select Data as the Type

- g) Enter 16 as the #Bits

- h) Enter the data (0101 1111 0101 1010b in this example)

- i) Click on the AP box to add a parity bit

- j) Add a description in the Description box if desired

| Table | size: [ | 1  | Bit Order: MS | SB 💌 Parity | y Control: | Reset | Parity | : Def | ault 🛛 🖌 💌         |

|-------|---------|----|---------------|-------------|------------|-------|--------|-------|--------------------|

|       | M1      | M2 | Туре          | Waveform    | #Bits      | -     | Data   | AP    | Description        |

| 1     | Н       | L  | Data          |             | 16         |       | 0x5F5A | ✓     | Single 16 bit word |

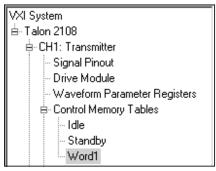

4.2.2.5.3.2 Two 40bit Words with Gap

In this example, the user wishes to output two 40bit words, (8 bit header followed by 32-bit data) separated by a 300 bit time fixed gap. Data is to be transmitted as LSB and parity is to be appended to the data. The steps are:

a) Right click on Control Memory Tables in the menu directory

b) Enter a name for the table, (Exam\_2 for this example)

- c) Enter 5 as the step size

- d) Select LSB for the Bit Order

- e) For Step 1 select Data as the Type

- f) Enter 8 as the #Bits

- g) Enter the data for header 1 ("0000 1111b" in this example)

- h) For Step 2 select Data as the Type

- i) Enter 32 as the #Bits

- j) Enter the data for word 1 ("0x73CA 73CA" in this example)

- k) Click on the AP box to append the parity bit

- I) For Step 3 select Gap as the Type

- m) Select GPR0 as the waveform to be transmitted as the Gap signal

- n) Enter 300 as the #Bits

- o) For Step 4 select Data as the Type

- p) Enter 8 as the #Bits

- q) Enter the data for header 1 ("0011 1100b" in this example)

- r) For Step 5 select Data as the Type

- s) Enter 32 as the #Bits

- t) Enter the data for word 1 ("0x9160 9103" in this example)

- u) Click on the AP box to append the parity bit

| Table | e size: | 5  | Bit Order: LS | B 💌 Paritj | y Control: | Reset Parity | g Def | ault Bank: A |  |

|-------|---------|----|---------------|------------|------------|--------------|-------|--------------|--|

|       | M1      | M2 | Туре          | Waveform   | #Bits      | Data 🗪       | AP    | Description  |  |

| 1     | L       | L  | Data          |            | 8          | OxOF         |       | Header       |  |

| 2     | L       | L  | Data          |            | 32         | 0x73CA73CA   | ✓     | Word 1       |  |

| 3     | L       | L  | Gap           | GPR0       | 300        |              |       | Gap          |  |

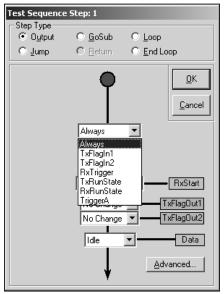

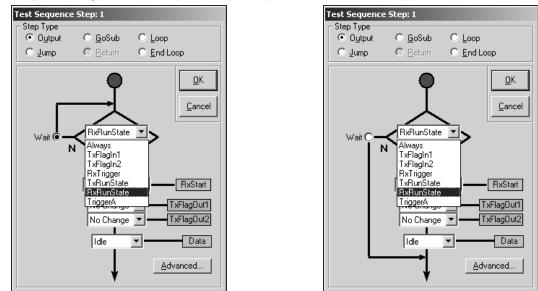

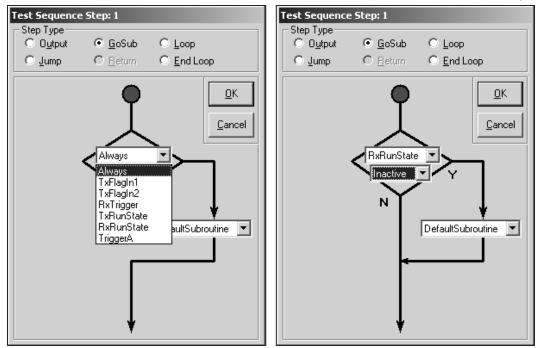

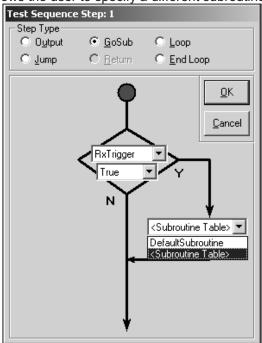

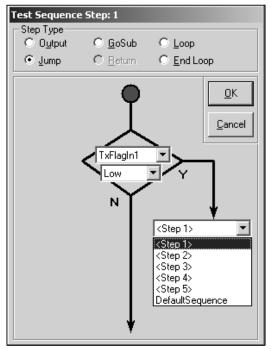

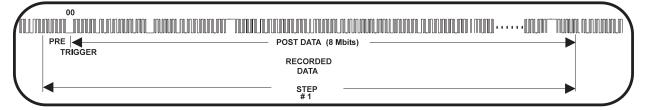

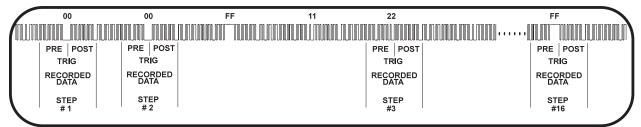

| 4     | L       | L  | Data          |            | 8          | 0x3C         |       | Header 2     |  |